### **THÈSE**

Pour obtenir le grade de

### **DOCTEUR DE L'UNIVERSITÉ GRENOBLE ALPES**

École doctorale : MSTII - Mathématiques, Sciences et technologies de l'information, Informatique

Spécialité : Informatique

Unité de recherche : Laboratoire de conception et d'intégration des systèmes

# Compilation pour la sécurité matérielle : au-delà de la sémantique Compilation beyond semantics for hardware security

Présentée par :

## Sébastien MICHELLAND

### Direction de thèse :

Laure GONNORD Directrice de thèse

PROFESSEURE DES UNIVERSITÉS, Grenoble INP – UGA

Christophe DELEUZE Co-encadrant de thèse

MAÎTRE DE CONFÉRENCES, Grenoble INP – UGA

### Rapporteurs:

Karine HEYDEMANN

SECURITY SENIOR EXPERT (HDR), Thalès CDI

Jens GUSTEDT

DIRECTEUR DE RECHERCHE, Centre Inria de l'Université de Lorraine

### Thèse soutenue publiquement le 24 octobre 2025, devant le jury composé de :

Laure GONNORD, Directrice de thèse

PROFESSEURE DES UNIVERSITÉS, Grenoble INP – UGA

Karine HEYDEMANN, Rapporteure

DOCTEURE EN SCIENCES HDR, Thalès DIS

Jens GUSTEDT, Rapporteur

DIRECTEUR DE RECHERCHE, Centre Inria de l'Université de Lorraine

Isabelle PUAUT, Examinatrice

PROFESSEURE DES UNIVERSITÉS, Université de Rennes

Marie-Laure POTET, Examinatrice

PROFESSEURE DES UNIVERSITÉS EMÉRITE, Grenoble INP – UGA

Albert COHEN, Examinateur

DIRECTEUR DE RECHERCHE, Google

Daniel GRUSS, Examinateur

UNIVERSITY PROFESSOR, Graz University of Technology

### Invités :

### Christophe DELEUZE

MAÎTRE DE CONFÉRENCES, Grenoble INP - UGA

# Résumé

Les systèmes informatiques sont construits par couches pour limiter leur complexité. Par exemple, le logiciel et le matériel sont globalement indépendants ; ils s'accordent sur une interface commune appelée « assembleur », et ensuite ignorent (*s'abstraient*) chacun des détails internes de l'autre. Cette construction décompose élégamment le système en éléments simples et est omniprésente en informatique ; il y a d'ailleurs une dizaine de ces couches d'abstraction entre le logiciel utilisé pour visualiser ce document et les lois fondamentales de la physique. Cependant, les interfaces successives entre couches n'isolent que les fonctionnalités, et pas par exemple les performances... ou la sécurité.

Les injections de faute sont des attaques matérielles qui induisent des comportements anormaux (fautes) en interférant volontairement avec des circuits (signaux, alimentation, champs électromagnétiques, etc.—tous les coups sont permis). Elles représentent une menace majeure pour les systèmes embarqués qui va au-delà de simples fautes aléatoires dues à des défauts de fabrication : ce sont des attaques ciblées qui peuvent exploiter même les faiblesses mineures dans un système. Et comme les abstractions ne se préoccupent pas de la sécurité, les contremesures ne peuvent pas être décomposées en couches ; elles doivent tenir compte de tout le système d'un seul coup, ce qui est sensiblement plus difficile.

De fait, il est déjà difficile de couvrir les couches logicielles, allant du code applicatif hautniveau typiquement écrit en C au code assembleur. Il est connu que *compiler* des programmes peut détruire les parties logicielles des contremesures de sécurité. Par exemple, pour sécuriser on peut faire les calculs sensibles en double et vérifier qu'il n'y a pas eu d'erreur causée par une faute ; le compilateur, ignorant la menace de sécurité, supprimera les doublons (jugés inutiles) pour optimiser les performances du programme. Cette relation antagoniste fait de la compilation sécurisée un deuxième domaine de l'informatique où des générateurs de texte produisent des résultats fonctionnellement valides mais fondamentalement inadéquats.

Cette thèse analyse cette friction entre les contremesures de sécurité (principalement contre les injections de faute) et la compilation de code C. J'y démontre que les menaces envers le code de sécurité sont inhérentes à la descente en abstraction et ne peuvent pas être esquivées juste en désactivant les optimisations, avec une analyse détaillée dans le cas du compilateur LLVM. J'expose également de multiples subtilités sémantiques qui rendent des certifications formelles improbables pour les primitives de sécurité dans un compilateur de production, ce qui motive une approche expérimentale.

La production centrale de la thèse est Tracing LLVM, une surcouche libre légère pour LLVM qui enrichit l'interface entre le code et le compilateur pour faciliter l'implémentation de contremesures de sécurité. J'illustre ces extensions sur une palette d'exemples et montre qu'on peut les composer pour obtenir un contrôle fin sur le code généré tout en écartant la majorité des menaces provenant des optimisations et descentes en abstraction. Au centre de cet outil est un système de « tracé » permettant de connecter des éléments du programme source avec les programmes intermédiaires, ce qui aide les contremesures à naviguer la pile d'abstraction.

Ces contributions au développement de la compilation sécurisée ouvrent des portes pour faciliter la co-conception logicielle/matérielle des mécanismes de défense contre les attaques matérielles et consolider leur sécurité.

# **Abstract**

Computer systems are built in layers to contain their complexity. For instance, software and hardware are mostly independent; they simply agree on a common interface called an "assembler" programming language, and then ignore (abstract away) each other's internal details. This brilliantly breaks down the system in manageable pieces and is used extensively; in fact, the program visualizing this document is probably a dozen such abstraction layers away from the fundamental laws of physics. However, these successive layers only abstract away the system's functionality, not other aspects like its performance... or its security.

Fault injections are hardware attacks that induce abnormal behaviors (*faults*) by interfering with circuits (through signals, power, electromagnetic fields, or otherwise—anything goes). They pose a major threat to embedded systems that's not just random defect-induced faults but targeted, engineered attacks that can slip through even minor cracks in a system. And since abstractions don't cover security, countermeasures can't be broken down into layers and need to cover the entire system at once, which is significantly more challenging.

In fact, just covering the software layers, spanning from high-level application code typically in C to assembler code, is difficult. It is well understood that *compiling* programs can destroy the software components of security countermeasures. For instance, it makes sense to run sensitive computations twice to check for errors induced by faults, but a compiler will proudly delete the duplicates, which are redundant in its functional-only abstract semantics. This adversarial relationship makes compiling for security a second field of computer science that struggles over generating text that is functionally valid yet substantially inadequate.

This thesis analyzes this friction between security countermeasures against hardware attacks (mostly fault injections) and the compilation of C code. I show that the threats to security code are inherent to the descent in abstraction and can't simply be dodged by disabling optimizations, with a detailed breakdown in the case of the widely-used production compiler LLVM. I also highlight many of the semantic subtleties that lie between security primitives and formally-provable security properties, motivating an experimental approach to the problem.

The central production of the thesis is Tracing LLVM, a lightweight open-source extension of LLVM which enriches the interface between program and compiler to facilitate the implementation of security countermeasures. I demonstrate these extensions on a variety of examples and show that they can compose to great effect, providing fine control over generated code while eliminating most threats from lowerings and optimizations. Key to this proposition is a new "tracing" system that assists in maintaining a connection between the source and intermediate programs, which helps countermeasures navigate the abstraction stack.

These contributions constitute a significant step towards security-aware compilation, which opens co-design opportunities and promising reliability improvements for defense mechanisms against these tricky hardware attacks.

# **Contents**

| Résumé 2 |       |                                                 |                                                             |          |  |  |

|----------|-------|-------------------------------------------------|-------------------------------------------------------------|----------|--|--|

| Ab       | strac | et                                              |                                                             | 3        |  |  |

| 1        | Intr  | oductio                                         | on                                                          | 7        |  |  |

|          | 1.1   | Hardw                                           | vare security                                               | 8        |  |  |

|          | 1.2   | Modei                                           | rn C compilers, LLVM IR, and RISC-V                         | 10       |  |  |

|          | 1.3   | Contri                                          | ibution and outline                                         | 12       |  |  |

|          | 1.4   | Disser                                          | nination                                                    | 13       |  |  |

| 2        | Inco  | mplete                                          | eness in the security stack                                 | 15       |  |  |

|          | 2.1   | Quick overview of fault and side-channel models |                                                             |          |  |  |

|          |       | 2.1.1                                           | Fault models                                                | 16       |  |  |

|          |       | 2.1.2                                           | Side-channel models                                         | 17       |  |  |

|          | 2.2   | Broad                                           | categories of security properties                           | 18       |  |  |

|          | 2.3   |                                                 | iques and design of hardening compilation                   | 20       |  |  |

|          |       | 2.3.1                                           | Hardening at every level in the toolchain                   | 20       |  |  |

|          |       | 2.3.2                                           | High-level design considerations                            | 23       |  |  |

|          |       | 2.3.3                                           | Overview of security modeling and proof                     | 25       |  |  |

|          | 2.4   | Preser                                          | ving security in the compilation chain                      | 25       |  |  |

|          |       | 2.4.1                                           | Compiler interference threatening security properties       | 26       |  |  |

|          |       | 2.4.2                                           | Techniques for property preservation                        | 27       |  |  |

|          |       | 2.4.3                                           | A few certified security properties                         | 29       |  |  |

|          |       | 2.4.4                                           | Preserving generic properties                               | 30       |  |  |

|          | 2.5   | Tracea                                          | ability in compilation                                      | 31       |  |  |

|          | 2.6   |                                                 | are/hardware co-design                                      | 31       |  |  |

|          |       | 2.6.1                                           | Improving performance                                       | 31       |  |  |

|          |       | 2.6.2                                           | Addressing micro-architectural fault models                 | 31       |  |  |

|          |       | 2.6.3                                           | Enriching the interface layer between software and hardware | 32       |  |  |

|          | 2.7   | Chapt                                           | er conclusion                                               | 32       |  |  |

| 3        | The   | vision:                                         | threading security through abstractions                     | 33       |  |  |

|          | 3.1   |                                                 | s of interest in the security process                       | 33       |  |  |

|          |       | 3.1.1                                           | Delimit uncertainties to facilitate unit validation         | 33       |  |  |

|          |       | 3.1.2                                           | Account for high-level security requirements                | 34       |  |  |

|          |       | 3.1.3                                           | Facilitate software/hardware co-design                      | 34       |  |  |

|          | 3.2   |                                                 | oution of responsibilities                                  | 35       |  |  |

|          | 3.3   | ·                                               |                                                             |          |  |  |

|          |       | 3.3.1                                           | Model of a secure build                                     | 36<br>36 |  |  |

|          |       | 3.3.2                                           | Potential for integration with the rest of the toolchain    | 38       |  |  |

|          |       | 3.3.3                                           | Lack of language support                                    | 38       |  |  |

|          | 3.4   |                                                 | oles and use cases                                          | 39       |  |  |

|          |       |                                                 | Strict variable accesses                                    | 40       |  |  |

CONTENTS 5

|   |     | 3.4.2                | Sequencing at variable writes                             | 41 |  |  |  |

|---|-----|----------------------|-----------------------------------------------------------|----|--|--|--|

|   |     | 3.4.3                | Avoid optimizations during lowerings                      |    |  |  |  |

|   |     | 3.4.4                | Map source variables to registers                         |    |  |  |  |

|   |     | 3.4.5                | Cleanup sensitive registers                               |    |  |  |  |

|   |     | 3.4.6                | Split register allocation                                 |    |  |  |  |

|   | 3.5 | Discus               | ssion of the examples                                     |    |  |  |  |

|   |     | 3.5.1                | End-to-end management of security                         |    |  |  |  |

|   |     | 3.5.2                | Threats from lowerings rather than optimizations          |    |  |  |  |

|   | 3.6 |                      | ter conclusion                                            |    |  |  |  |

| 4 | Cou | ntorm                | easures at the lowest levels of software                  | 50 |  |  |  |

| 4 | 4.1 |                      |                                                           |    |  |  |  |

|   | 4.1 | 4.1.1                | alizing fetch skips                                       |    |  |  |  |

|   |     | 4.1.1                |                                                           |    |  |  |  |

|   |     |                      | Informal description of fetch skips                       | 52 |  |  |  |

|   | 4.2 | 4.1.3                | Operational semantics of RISC-V programs with fetch skips |    |  |  |  |

|   | 4.2 |                      | designed countermeasure                                   |    |  |  |  |

|   |     | 4.2.1                | Overview                                                  |    |  |  |  |

|   |     | 4.2.2                | ISA and hardware extensions                               |    |  |  |  |

|   |     | 4.2.3                | Hardening algorithm                                       |    |  |  |  |

|   |     | 4.2.4                | LLVM implementation                                       |    |  |  |  |

|   |     | 4.2.5                | Discussion                                                |    |  |  |  |

|   | 4.3 |                      | ity theorem                                               |    |  |  |  |

|   |     | 4.3.1                | Security guarantee against multi-fault executions         |    |  |  |  |

|   |     | 4.3.2                | Security guarantee against single-fault executions        |    |  |  |  |

|   | 4.4 |                      | mentation setting and evaluation                          |    |  |  |  |

|   |     | 4.4.1                | Implementation and experimental setting                   |    |  |  |  |

|   |     | 4.4.2                | Functional correctness                                    |    |  |  |  |

|   |     | 4.4.3                | Security guarantee                                        |    |  |  |  |

|   |     | 4.4.4                | Performance                                               |    |  |  |  |

|   | 4.5 | 5 Chapter conclusion |                                                           |    |  |  |  |

| 5 | Wri | ting co              | ountermeasures with Tracing LLVM                          | 68 |  |  |  |

|   | 5.1 | Tracin               | ng LLVM                                                   | 68 |  |  |  |

|   |     | 5.1.1                | Project description                                       | 68 |  |  |  |

|   |     | 5.1.2                | Overview of the main features                             | 69 |  |  |  |

|   | 5.2 | Featur               | re descriptions                                           | 70 |  |  |  |

|   |     | 5.2.1                | Opacification function                                    | 71 |  |  |  |

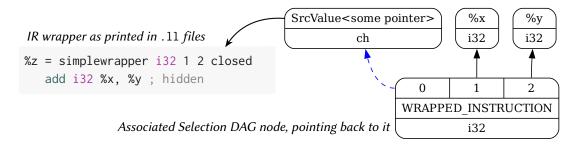

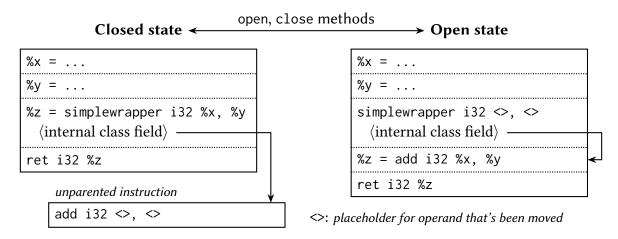

|   |     | 5.2.2                | Wrapper instructions                                      | 71 |  |  |  |

|   |     | 5.2.3                | Traced types                                              | 73 |  |  |  |

|   |     | 5.2.4                | Tracing variables                                         | 74 |  |  |  |

|   |     | 5.2.5                | Tracing dataflow                                          | 75 |  |  |  |

|   |     | 5.2.6                | Wrapper lowering                                          | 75 |  |  |  |

|   |     | 5.2.7                | Register allocation for tracing                           | 76 |  |  |  |

|   | 5.3 | Examp                | ples and use cases                                        | 76 |  |  |  |

|   |     | 5.3.1                | Strict variable accesses                                  | 76 |  |  |  |

|   |     | 5.3.2                | Sequencing at variable writes                             | 77 |  |  |  |

|   |     | 5.3.3                | Avoid optimizations during lowerings                      | 78 |  |  |  |

|   |     | 5.3.4                | Map source variables to registers                         |    |  |  |  |

|   |     |                      | $oldsymbol{arphi}$                                        |    |  |  |  |

6 CONTENTS

|     |                                                | 5.3.5   | Cleanup sensitive registers                           | . 81           |  |  |  |  |

|-----|------------------------------------------------|---------|-------------------------------------------------------|----------------|--|--|--|--|

|     |                                                | 5.3.6   | Split register allocation                             | . 83           |  |  |  |  |

|     | 5.4                                            | Applic  | ation to a full PIN verification program              | . 83           |  |  |  |  |

|     |                                                | 5.4.1   | Initial source code                                   | . 84           |  |  |  |  |

|     |                                                | 5.4.2   | Countermeasures inserted and failed initial build     | . 85           |  |  |  |  |

|     |                                                | 5.4.3   | Secure build using Tracing LLVM features              |                |  |  |  |  |

|     |                                                | 5.4.4   | Discussion                                            |                |  |  |  |  |

|     | 5.5                                            | Chapte  | er conclusion                                         |                |  |  |  |  |

| 6   | Implementation and integration of Tracing LLVM |         |                                                       |                |  |  |  |  |

| U   | 6.1                                            |         | ng in LLVM                                            | <b>89</b> . 89 |  |  |  |  |

|     | 0.1                                            |         |                                                       |                |  |  |  |  |

|     |                                                | 6.1.1   | Constraints and targets                               |                |  |  |  |  |

|     | <i>(</i> 2                                     | 6.1.2   | Maintenance and research tools                        |                |  |  |  |  |

|     | 6.2                                            |         | ng non-functional features in LLVM                    |                |  |  |  |  |

|     |                                                | 6.2.1   | Debug information                                     |                |  |  |  |  |

|     |                                                | 6.2.2   | Inline assembly                                       |                |  |  |  |  |

|     |                                                | 6.2.3   | Hacks                                                 |                |  |  |  |  |

|     | 6.3                                            |         | ques to extend or constrain representations           |                |  |  |  |  |

|     |                                                | 6.3.1   | Intended language extensions                          |                |  |  |  |  |

|     |                                                | 6.3.2   | States allowed by API not exploited by implementation | . 95           |  |  |  |  |

|     |                                                | 6.3.3   | Constrained shapes within existing languages          | . 96           |  |  |  |  |

|     |                                                | 6.3.4   | Divert existing features                              | . 96           |  |  |  |  |

|     | 6.4                                            | Summ    | ary of changes made to LLVM                           | . 96           |  |  |  |  |

|     | 6.5                                            | Chapte  | er conclusion                                         | . 97           |  |  |  |  |

| 7   | Out                                            | line of | guarantees and validation methods                     | 98             |  |  |  |  |

|     | 7.1                                            |         | and tools for validation                              | . 98           |  |  |  |  |

|     | 7.2                                            |         | ties desired from opacification                       |                |  |  |  |  |

|     | 7.3                                            |         | ormations weakening opacification guarantees          |                |  |  |  |  |

|     | 7.4                                            |         | ary of expectations and threats for opacification     |                |  |  |  |  |

|     | 7.5                                            |         | ptions underlying the design of Tracing LLVM          |                |  |  |  |  |

|     | 7.6                                            |         | er conclusion                                         |                |  |  |  |  |

| 0   | Can                                            | •       | and future work                                       | 110            |  |  |  |  |

| 8   | Con                                            | Clusion | rand future work                                      | 110            |  |  |  |  |

| A   | Proof of the fetch skips hardening theorem     |         |                                                       |                |  |  |  |  |

|     | A.1                                            | Detaile | ed instruction semantics                              | . 112          |  |  |  |  |

|     | A.2                                            | Harde   | ning algorithm and proof of security                  | . 114          |  |  |  |  |

|     |                                                | A.2.1   | Additional definitions on blocks                      | . 114          |  |  |  |  |

|     |                                                | A.2.2   | Feasibility of Algorithm HARDEN                       | . 114          |  |  |  |  |

|     |                                                | A.2.3   | Structure of hardened programs                        | . 115          |  |  |  |  |

|     |                                                | A.2.4   | Program state upon leaving a hardened block           |                |  |  |  |  |

|     |                                                | A.2.5   | Security guarantees                                   |                |  |  |  |  |

| Bi  | bliog                                          | raphy   |                                                       | 125            |  |  |  |  |

|     |                                                |         | Tables and Distinct                                   | 136            |  |  |  |  |

| LIS | List of Figures, Tables and Listings           |         |                                                       |                |  |  |  |  |

| In  | Index 1                                        |         |                                                       |                |  |  |  |  |

# Introduction $\int$

Benjamin Lee Whorf (1897–1941), American linguist and chemical engineer

Image credit: The Hartford Agent Magazine/Benjamin Lee Whorf Papers, Manuscripts and Archives, Yale University Library (ID 10009314)

s I landed on the core conclusion from this thesis, I was surprised to find that it seemed to be captured by a specific linguistic theory, if it were applied to programming languages. It piqued my interest enough for the following modest attempt at establishing this relationship.

There is a concept in linguistics that language doesn't just describe our perception of reality, but also influences it; that our constant use of language for classifying and communicating the world warps our perceptions so they fall neatly into what our spoken language can describe. This principle is commonly associated with Benjamin Lee Whorf [Who97], popularized by quotes such as "Language shapes the way we think" (though he did not invent it).

This notion of has been the subject of intense debate. The idea is often split into two separate flavours [Cha94]; the strong *linguistic determinism* hypothesis that our thinking is determined by language, and the weak *linguistic relativity* hypothesis that language influences our perception and interpretation of the world. Nowadays, there appears to be a general agreement against the strong hypothesis, while the weak one remains debated.

One might wonder whether linguistic relativity applies to programming languages (after all, programming and linguistics often intersect, such as with the theories of grammar and parsing). And there is, indeed, no shortage of testimony that varied programming paradigms lend themselves to equally varied formalizations of real-world problems, influencing developers' intuitive models and solutions. Jenna Zeigen addresses this question in a talk [Jen14] where she casts a mould of linguistic relativity around Paul Graham's "Blub Paradox" (from his talk-then-essay "Beating the Averages" [Gra01]).

One important distinction is that Whorf aimed to "calibrate" spoken languages such as English and Hopi with each other, allowing translations between their differing perceptions of the same reality. On the other hand, Zeigen's and Graham's discussion is underpinned by the claim that there is an order of power in programming languages, and that this order is abstraction; Graham writes, "if you have a choice of several languages, it is, all other things being equal, a mistake to program in anything but the most powerful one".

In this thesis I explore problems related to security, which, as it turns out, makes all other things very much not equal. Studying programming languages and their compilation under the lens of non-functional requirements forces us to capture the complexity of the entire language stack. So there is no single language to solve hardware security, let alone high-level.

In essence, my central claim is that low-level security concerns escape the modeling power of high-level programming languages, which only capture a chosen subset of functionality. Each lower abstraction level may attempt to cast the threat into a form that the next level can perceive accurately and counter. But on a basic level, the technical framework of countermeasures against hardware vulnerabilities is defined by the strong principle of linguistic determinism applied to computing abstractions, each being constrained in its perception of the threat by its limited ability to model the system.

# 1.1 Hardware security

Computer systems today are built in layers. We start with transistors on a chip and create logic gates and memories. From then on, we forget about the transistors, and directly use the gates and memories to create processors. We gradually go higher by building more abstract stages on the interfaces of lower stages. At some point, we start writing software in the processor's assembly language while ignoring the processor's implementation. Eventually, we forget the assembler too and write programs in "high-level" programming languages like C that we compile to assembler automatically. Each new layer is an *abstraction* of the previous, hiding tedious implementation details while providing more expressive tools for building complex systems.

This design has many advantages, chief among which is breaking down the complexity of computers over multiple fields of engineering. Hardware designers can change microarchitectures, and so long as they use the same assembly language, existing software will keep working, stabilizing the work of software engineers. This is why I can write the dot product function of Listing 1.1 in C and be confident it'll run on pretty much anything.

```

long dot(int *x, int *y, size_t n) {

long result = 0;

for(size_t i = 0; i < n; i++)

result += x[i] * y[i];

return result;

} /* did you spot the bug? */</pre>

```

Listing 1.1: Integer dot product function in C

There are limits, of course; each stage is designed to abstract the *functionality* of lower stages, but can't guarantee other properties, called "non-functional", such as *performance* and *security*. Looking at Listing 1.1 again, the C language specifies exactly what the multiplication operator computes, but not how long it takes to produce its result. The performance characteristics of the program depend greatly on the processor's implementation.

Thus, systems with non-functional requirements cannot rely on abstractions alone and must be aware of internal software and hardware details. This thesis is concerned with the particular case of hardware security vulnerabilities, which come in two flavours.

**Fault injection attacks** are physical attacks that deliberately cause *faults* in the system.

1.1. HARDWARE SECURITY 9

A fault is any abnormal condition that leads to incorrect behavior. Traditionally the threat of faults was limited to manufacturing defects or extreme operating conditions (famously illustrated with cosmic rays flipping bits in avionics), but the development of *fault injection* techniques [She+21] made them an explicit attack vector.

On Listing 1.1, a typical fault attack might lead to an assembler instruction being skipped. Depending on the precise assembler code, this could skip a product, an accumulation step, use a wrong operand somewhere, end the loop early, extend it, use data or run code from other functions, and many other effects. This variety is a key reason why fault attacks constitute a significant threat. Occasionally a particularly impactful fault attack reaches the mainstream public, like Rowhammer [Kim+14] which had the rare ability to target servers remotely.

**Side-channel attacks** are passive attacks that exploit sensitive information extracted from a system without compromising its execution. A side-channel is any physical observation of the system that is correlated with its internal operations, like timing, power consumption, or all sorts of internal processor state that can be observed indirectly.

Again with Listing 1.1, the multiplication instruction on the targeted processor might be faster for small inputs, allowing attackers to learn information about the values of x and y by measuring execution times. If either of the arrays contains secret data, this would constitute a severe breach of confidentiality. Side-channel attacks also frequently go mainstream, like the haunting legacy of Spectre's [Koc+19] speculative execution leaks, or more recently when Apple processors' aggressive optimizations led to the GoFetch vulnerability [Che+24].

This combination of factors—extreme non-functionality and endless physical variations—makes hardware vulnerabilities particularly difficult to deal with. No one I've met entertains the notion of a complete defense against known attacks, let alone future ones. Obviously this expectation of incompleteness doesn't preclude the study and deployment of countermeasures, but it makes any *guarantees* about behaviors or coverage that much more valuable.

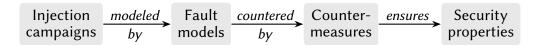

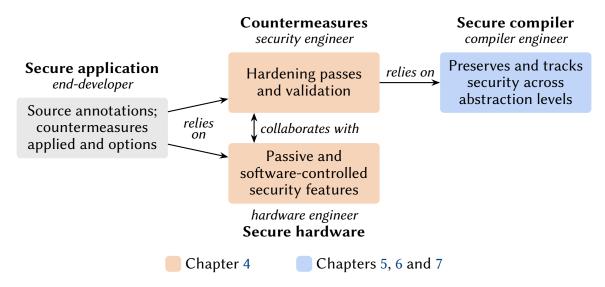

Figure 1.2 shows the process for designing a countermeasure against a fault attack, which will be our main use case. Just like how functional abstractions are spread over different fields of specialty, modeling vulnerabilities and designing countermeasures involves experts at many levels of the system.

Figure 1.2: Usual process for countering a fault injection attack

- 1. First, hardware experts run *injection campaigns* with appropriate equipment and collect faulted execution traces.

- 2. Then they formulate a *fault model* that summarizes the most common effects and describes them at a higher level of abstraction.

- 3. From there, hardware or software engineers devise mechanisms for nullifying, detecting, or recovering from the attack, which can be in hardware, in software, or both.

- 4. Deploying the countermeasure then guarantees that a specific security property holds even when attacked, typically some sort of integrity or confidentiality requirement.

The main challenge at the moment remains providing countermeasures that are effective against attacks without large performance or resource overheads. The rapid improvement of

attacks means that protections are often not yet secure enough [Yuc+16]—sometimes fundamentally insufficient [Ran23]—all while the industry of embedded systems puts a premium on cost-effectiveness. My work tackles two aspects of the reliability objective: countering accurate fault models, and eliminating friction around the compilation of countermeasures.

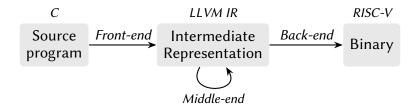

# 1.2 Modern C compilers, LLVM IR, and RISC-V

A central part of this thesis is understanding and improving the interactions between compilers and security countermeasures. A compiler is a tool that translates programs from a high-level programming language to another, lower-level programming language. In the context of embedded systems, engineers will most commonly write their software in C then compile it to assembler so it can be run on real hardware.

C is not a particularly high-level programming language; it may well be the lowest among those used to write large-scale applications. Developers can often predict what assembler code a compiler is likely to generate, leading to a sense that the compiler produces "the" assembler code for any given C program<sup>1</sup>. However, modern compilers only guarantee that they'll output *some* assembler program whose functionality matches the C source, with no guarantees on its specific implementation, performance or security.

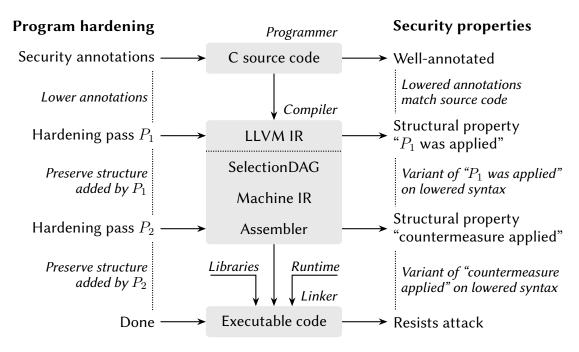

This rewriting process takes the program through multiple intermediate languages which were introduced over the years either for optimization or software engineering purposes. Optimizing compilers are generally centered around one internal language called the *Intermediate Representation* or IR (sometimes multiple of them). This naturally leads into a separation of the compiler into three different stages:

- the front-end, which rewrites the source into the intermediate representation;

- the *middle-end*, which optimizes the intermediate representation;

- and the *back-end*, which finally rewrites the program into target code.

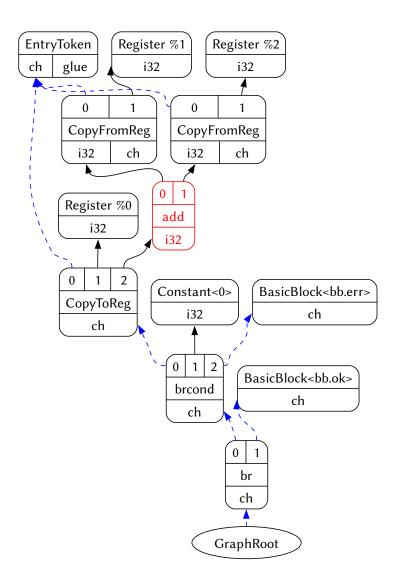

The steps that rewrite the program into a lower-level language or representation are called *lowerings*. We'll encounter a few more when delving into LLVM's back-end (Figure 5.2).

In our case, the source code is C and the target code is RISC-V assembler, but the design is intended to allow any supported source language to be compiled to any supported target language, by exploiting the same shared middle-end logic, which is the core of the compiler. (Although, when it comes to security, all components will be about equally relevant.)

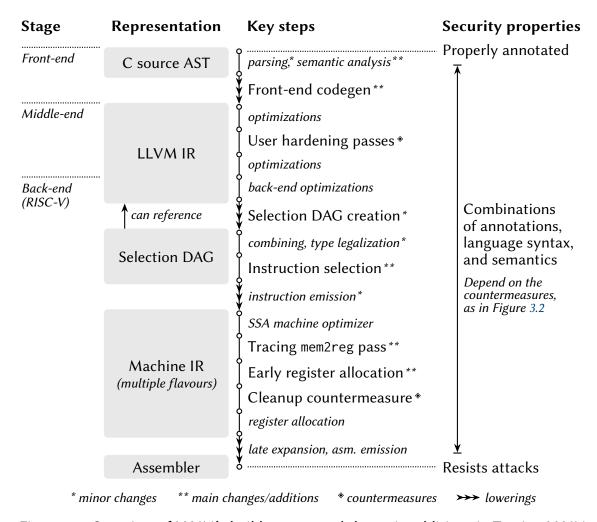

Figure 1.3: Bird's-eye view of compilation stages

LLVM's intermediate representation is called *LLVM IR*. Figure 1.4 (left) shows the (simplified) LLVM IR code for the dot product function after the front-end and middle-end have run.

<sup>&</sup>lt;sup>1</sup>For a notable example, consider https://www.youtube.com/watch?v=MShbP30pASA&t=21m58s.

### LLVM IR code (simplified)

```

define i32 @dot(ptr %x, ptr %y, i32 %n) {

2

%empty = icmp eq i32 %n, 0

3

4

br i1 %empty, label %end, label %loop

5

loop:

6

7

%i = phi i32 [%new_i, %loop], [0, %entry]

%result = phi i32 [%new_result, %loop],

8

[0, %entry]

9

%xiptr = getelementptr i32, ptr %x, i32 %i

10

%xi = load i32, ptr %xiptr, align 4

11

%yiptr = getelementptr i32, ptr %y, i32 %i

12

%yi = load i32, ptr %yiptr, align 4

13

%xiyi = mul i32 %xi, %yi

14

15

%new_result = add i32 %xiyi, %result

new_i = add i32 \%i, 1

16

%exit = icmp eq i32 %new_i, %n

17

br i1 %exit, label %end, label %loop

18

19

20

end:

%res = phi i32 [0, %entry],

21

22

[%new_result, %loop]

23

ret i32 %res

24

}

```

# entry end one end one

### RISC-V assembler code

```

1

2

# a0 is x, a1 is y, a2 is n

3

li

a3, 0

4

begz

a2, .end

5

.loop:

6

lw

a4, 0(a0)

# a4 = *x

7

lw

a5, 0(a1)

# a5 = *y

a4, a5, a4

8

mul

9

add

a3, a3, a4

a2, a2, -1

10

addi

# n--

11

addi

a1, a1, 4

# V++

a0, a0, 4

12

addi

# x++

13

bnez

a2, .loop

14

.end:

15

mv

a0, a3

16

# returns a0

ret

```

Figure 1.4: Dot product: LLVM IR code, control-flow graph, and RISC-V code

Unlike C functions, LLVM IR functions do not have nested control-flow structures; they consist of a flat list of *basic blocks* (here entry, loop and end). Each basic block is made of a sequence of straight-line instructions, ending either in a jump to another block, a conditional branch to two other blocks, or a function return. This induces a *Control-Flow Graph* (CFG) whose nodes are the basic blocks and edges are the possible jumps and branches between them, also shown in Figure 1.4 (top right).

A key feature of LLVM IR is that it is in *Static Single Assignment* (SSA) form [RT22]. This means that every variable in the function is assigned only once; intuitively speaking, a second assignment would be considered a new variable. If there are conditional assignments, multiple "versions" of the same variable can reach a given control point. For instance, on Figure 1.4 when entering the loop body on line 7, i might be 0 (if we came from the entry block) or from the incremented value %new\_i generated by the previous iteration (if we came from the loop body). This kind of conflict is reconciled using a special phi operator which redefines the variable based on the control path at runtime. Essentially, the SSA form determines what versions of variables are visible to each statement and encodes it explicitly. We won't see much of phi in this thesis, but the splitting aspect in worth keeping in mind.

Other than its specific format using SSA in a control-flow graph, LLVM IR mostly resembles three-address code annotated with types (i32 being 32-bit integers and i1 being booleans). The LLVM IR code we'll see will focus on basic instructions such as memory loads (load) or

arithmetic (add, xor, etc.). For more detail, please see the LLVM language reference<sup>2</sup>.

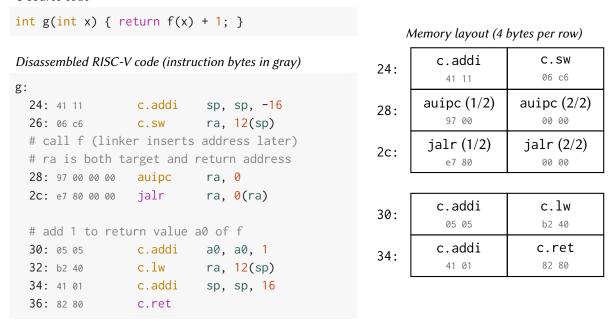

Figure 1.4 also shows the RISC-V assembler code produced by the compiler's back-end (bottom right). RISC-V is an open-standard Instruction Set Architecture<sup>3</sup>; for our purposes, it mostly defines an extensible assembler language. It is a fairly standard RISC architecture; for the purpose of reading this thesis, the following aspects of 32-bit RISC-V are relevant:

- The main registers are a0–a7 (*arguments*, caller-saved/scratch), t0–t6 (*temporaries*, caller-saved/scratch) and s0–s11 (*saved*, callee-saved/permanent).

- Special registers mostly include the return address ra and stack pointer sp.

- Output operands, if any, come first.

- The notation "off(reg)" refers to the memory address or operand at reg+off.

- Arguments are passed in a0, a1, etc.; the return value is a0.

The following instructions will make an appearance:

- Moving values: mv (MoVe), 1i (Load Immediate);

- Memory accesses: lw (Load Word), sw (Store Word), lbu (Load Byte Unsigned);

- Unconditional control-flow: j[r] (Jump [Register]), call, ret;

- Conditional control flow: beq (Branch if EQual), beqz (Branch if EQual to Zero), and variations with other two-letter comparison codes;

- The usual arithmetic: add, mul, xor, etc.

The assembler code for the dot product function should hopefully be straightforward. Note however how the logic differs from the IR code; i has been eliminated, instead the pointers x and y (a0 and a1) are incremented at each iteration, and the counting is performed by decrementing n (a2) directly.

This example already illustrates some misconceptions about compilation. A user invoking LLVM would provide the C code as input and obtain the RISC-V assembler as output, and might assume that result was simply mapped to register a3, setting up the expectation that a single C variable would reasonably be assigned to a single register. However, the IR code hidden inside the compiler reveals that this is not the case, as both assignments to result are considered different variables. The fact that both end in a3 is not random, but it's also not guaranteed (and we'll see it in action later).

This kind of discrepancy severely limits programmers' ability to incorporate security countermeasures in programs or ensure that they get compiled in a satisfying manner. It's emblematic of the tension between functionality-oriented compiler design, and the real but unmodeled threats that countermeasures attempt to defeat. Fortunately, there are a few things we can do about that.

### 1.3 Contribution and outline

This thesis addresses the general problems of designing countermeasure for low-level attack models, and improving the reliability of secure code generation with a compiler.

Chapter 2 surveys the methods for writing security countermeasures in software, with a focus on compiler integration. Its main point is that approximations in fault models combined with

<sup>2</sup>https://llvm.org/docs/LangRef.html

<sup>&</sup>lt;sup>3</sup>https://riscv.org/. RISC stands for "Reduced Instruction Set Computer".

1.4. Dissemination 13

semantic subtleties in countermeasures make it hard to obtain strong guarantees, and that compiler "tricks" are insufficient.

Chapter 3 lays out my vision for improving the reliability of fault injection countermeasures, from design to implementation and validation (on the software side). This consists of two axes: (1) exploiting the lowest-level attack models possible, and (2) improving the reliability of secure compilation. It also contains examples demonstrating typical security violations that arise from compilation.

Chapter 4 addresses the first axis by demonstrating the use of semantic modeling to capture low-level effects in a fault injection countermeasure. In this chapter, I develop, implement, and validate a software/hardware co-designed countermeasure against a tricky attack model called *fetch skips*. The countermeasure builds upon a semantic model and I formally prove its security in Appendix A.

Chapter 5 and onwards address the second axis by describing different aspects of Tracing LLVM, my LLVM mod that extends languages and compiler to facilitate the implementation of security countermeasures. Chapter 5 describes Tracing LLVM from the perspective of a countermeasure developer, illustrates how it solves the examples from Chapter 3, and showcases a combination of four countermeasures on a longer PIN verification example.

Chapter 6 takes a short dive into the research questions that arise from the implementation of Tracing LLVM, mainly relating to language design and maintainability. These choices are key to extracting guarantees out of LLVM extensions without requiring complete knowledge of its multi-million-line codebase.

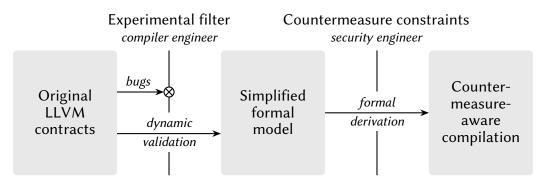

Finally, Chapter 7 takes a critical look at the interface between the compiler and the security assumptions made by countermeasures to prepare for a proper formalization in future work. I discuss the goals that such an interface should achieve, then illustrate the delicate rift between experimentally-predictable behaviors and formal guarantees with a series of theoretical but legal security-breaking program transformations.

Chapter 8, as one would expect, wraps up by summarizing the contributions and lays out future work for this project.

### What to read?

- If you want to understand Tracing LLVM's design and how to use it, read Chapters 3 and 5.

- For the research questions surrounding secure compilation, read Chapters 3 and 5 to 7.

- For countermeasures, read Chapter 4 (free-standing) or Chapters 3 and 5 (Tracing LLVM).

Chapter 2 provides valuable context but is not a hard dependency of other chapters; any relevant terms that it defines for later are listed in the index at the end of the document. The index collects definitions for the most common terms as well as thematic references for recurring concepts.

### 1.4 Dissemination

The proven countermeasure from Chapter 4 was the subject of a publication and presentation at the Compiler Construction conference of 2024 (CC'24) [MDG24]:

• Sébastien Michelland, Christophe Deleuze, and Laure Gonnord. "From low-level fault modeling (of a pipeline attack) to a proven hardening scheme". In: *Compiler Construction*

```

(CC'24). Edinburgh (Scotland), United Kingdom, Mar. 2024.

DOI: 10.1145/3640537.3641570. URL: https://hal.science/hal-04438994.

```

At the time of submitting this thesis, the Tracing LLVM bases described in Chapters 5–7 are cycling the submission pipeline.

This thesis happened in relation to the PEPR project ARSENE<sup>4</sup> (« *Architectures Sécurisées pour le Numérique Embarqué* », or "Secure Architectures for Embedded Computing") which aims to design sovereign secure platforms for embedded systems with a RISC-V base. The ARSENE project is funded by the "France 2030" government investment plan managed by the French National Research Agency, under the reference ANR-22-PECY-0004.

The state-of-the-art from Chapter 2 is based on a deliverable from the ARSENE project (reusing only the sections that I personally wrote).

I gave a number of talks on the subject of secure compilation:

- At the 2024 Journée thématique sur les Attaques par Injection de Fautes (JAIF) workshop (Rennes, France);

- At the 2025 PHISIC workshop (Gardanne, France);

- At French national community meetings: Journées GLsec (Paris, Nov. 2022), Journées du GDR Sécurité (Caen, June 2025)

- At a number of local seminars: CASH team (Lyon, Feb. 2024), ANSSI (March 2024), the Verimag lab (Grenoble, April 2024), CyberAlps seminar (Grenoble, May 2024), SemSécuÉlec seminar (Rennes, Sept. 2024), ÉPICURE team (Rennes, Sept. 2024), PACAP team (Rennes, April 2024) and finally Verimag again (Grenoble, June 2025).

In parallel to the work described in this document, I also completed a previous research project relating to the modeling of static analyzers in monadic semantics. This work was published and presented at the 2024 Internal Conference on Functional Programming (ICFP'24) [MZG24]:

• Sébastien Michelland, Yannick Zakowski, and Laure Gonnord. "Abstract Interpreters: A Monadic Approach to Modular Verification". In: *Proceedings of the ACM on Programming Languages* 8.ICFP (Aug. 2024), pp. 1–28.

```

DOI: 10.1145/3674646. URL: https://hal.science/hal-04628727.

```

This avenue of research is related to hardware security through its potential for formal verification, which other brilliant people have started to explore [Pes+25].

<sup>4</sup>https://www.pepr-cyber-arsene.fr/

# Incompleteness in the security stack

oftware protections against hardware vulnerabilities face a variety of challenges. This chapter covers the state-of-the-art of these software components, with an emphasis on countermeasures against fault injection attacks. The particular angle I want to highlight is how the challenges in defeating attacks manifest in the incompleteness of protections. This highlights why any guarantees are really valuable and motivates the focus of this thesis in improving reliability.

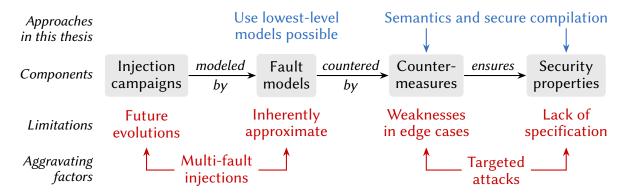

Figure 2.1: Limitations in the process for countering fault attacks

Figure 2.1 extends Figure 1.2 with the main hurdles in designing countermeasures against fault injection attacks.

- As before, injection campaigns are first run to sample execution traces. This analysis needs

continuous updates as the set of faults that can be reliably injected by attackers keeps

evolving.

- The fault model is then formulated; by construction it ignores rarer outcomes, and lifts the fault's description to a higher level of abstraction. Both effects lose real outcomes (and may introduce unrealistic ones), so the attack being protected against isn't *quite* the real attack.

- The step of building countermeasures doesn't have inherent weaknesses, but it's difficult to design protections that are complete even in edge cases. Broadly speaking due to community fragmentation countermeasures either counter accurate low-level models, or are formalized and proven, but rarely both.

- And a minor point, there is no unified framework for expressing security properties. They are often under-specified, with functional correctness as the implicit default.

These hardships are compounded by aggravating factors such as multi-fault injections (which add to the variety of attack methods and seriously complicates modeling) and targeted attacks (which may turn any single weakness into a serious vulnerability).

With this in mind, let's explore how literature deals with software contributions to this field. Starting with the requirements, Section 2.1 reviews usual attack models and Section 2.2 lists and attempts to categorize common targeted security properties. Section 2.3 covers the design of countermeasures, including their placement in the compiler and an overview of proof methods. Section 2.4 explores in more depth the problem of preserving security during compilation, which is tightly related to matters of *traceability* addressed in Section 2.5. I end with an overview of co-designed countermeasures in Section 2.6.

# 2.1 Quick overview of fault and side-channel models

Fault injection techniques are quite varied: some methods require contact on pins, such as clock/voltage glitches or body bias; some don't, like laser/X-ray pulses or electromagnetic interference. In this thesis, we only consider *transient* faults, which cause incorrect behaviors but do not actually damage the target (as opposed to *permanent* faults). The interested reader is referred to Shuvo et al. [Shu+23] for a more thorough listing.

Side-channels are similarly diverse; attackers can target programs' execution time [Koc96; HWH13; RG24], power consumption over time [Man03], or even electromagnetic emissions [QS01; SLS19]. All sorts of micro-architectural state affected by speculation is also a target, commonly categorized under the umbrella of Spectre [Koc+19] (and, to a lesser extent, Meltdown [Lip+20]). Leaks can further be analyzed over multiple executions by statistical methods for improved precision; such techniques include Correlation Power Analysis [BCO04] or Differential Power Analysis [KJJ99; Wan+17].

In both cases the complexity of the attacks calls for simplified models to smooth out the physical details and lift possible outcomes to higher abstraction levels. A single attack can be approximated by many models; generally speaking a higher-level model is easier to study and counter but a lower-level model better describes the possible outcomes of the attack. Note that approximations go both ways: they remove real behaviors (leading to worse protections) but also add fictional ones (leading to more expensive protections). Chapter 4 of this thesis will advocate for using the lowest-level models we can handle to avoid irrecoverable approximations.

### 2.1.1 Fault models

The following are common fault models, roughly sorted by decreasing abstraction level.

At source level:

- "Statement skip": skip a C statement (also confusingly called "instruction");

- **Branch inversion**: a conditional statement's targets are swapped [Pot+14];

- Corrupted control flow: arbitrary jumps in a function [HLB19]; calls to invalid targets...

At assembler/ISA level:

- **Instruction skip/re-execution**: an instruction is either skipped or executed twice [VHM03];

- **Branch inversion**: targets of a conditional branch instruction are swapped;

- **Bus corruption**: data read or written corrupted en route on the CPU/memory bus [DSL17].

- Wrong CFG edges: a branch instruction jumps to the start of an arbitrary block in the function CFG, even if there was no CFG edge there [HLB19];

- **PC corruption**: bit flip or other types of corruption of the PC register;

- **Architectural SEU** (Single Event Upset): bit flip in an architectural component, like a register [Bar+14b], memory location, or instruction opcode;

### At lower levels:

- Forwarding error: pipeline forwarding triggers when it shouldn't or doesn't when it should [Lau20];

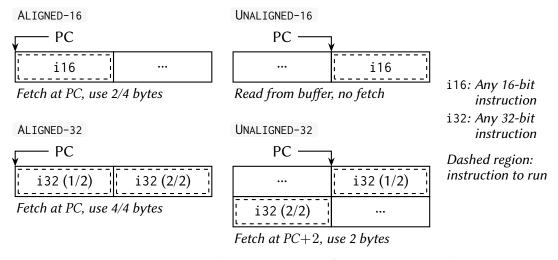

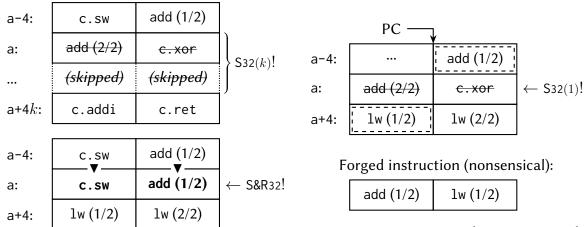

- **Fetch skip** and **skip-and-repeat**: skip or repeat a CPU fetch's worth of code data (e.g. 4 bytes), leading to a single or multiple instructions decoding incorrectly [Als+21];

- Low-level SEU (Single Event Upset): bit flip in RTL latches [Tol+22];

- **Partial** or **delayed update**: an RTL register has only part of its bits updated, or it updates a cycle later than it should [Als+24];

- Transistor failure: a transistor assumes a semi-permanent state [Anc+17].

For each of these models, one can also consider *multi-fault* variations where more than one fault may occur. Generally speaking, multiple simultaneous faults greatly increase the burden of modeling while multiple faults spread over time mostly complicates countermeasures.

The term "soft error" was also frequently used in early works to describe any potential misexecution of a program, but the interpretation of the term tends to vary from one publication to the next. It often ends up meaning a Single Event Upset (SEU, bit flip) but the abstraction level at which the SEU is considered still isn't always clear.

The chosen abstraction level for models is a clear accuracy-versus-simplicity trade-off; low-level descriptions are more true to practical attacks, but high-level approximations make it practical (in many cases *possible*) to reason about and protect against them. As it turns out, ISA-level models aren't always precise enough; faulted behaviors often depend on micro-architectural features and can only be described accurately by including hardware details [Lau+18]. Pipeline analysis by Yuce et al. [Yuc+16] further shows that targeted fault attacks can and do defeat many ISA-level countermeasures by exploiting unmodeled low-level effects. In other words, finer, more accurate countermeasures are still needed.

### 2.1.2 Side-channel models

While not a focus of this thesis, side-channel models serve the same purpose as fault models. Like faults, leaks of secret information can be difficult to analyze as they can be hidden by complex correlations. [Mar18] explains how countermeasures and other signal noises designed to defend against power analysis can be circumvented using different techniques including multidimensional probabilistic representation [CRR03; Arc+06].

Simple examples would be the *Hamming Weight* [Bel+13] and *Hamming Distance* models for power analysis. The Hamming weight model states that an attacker can observe the number of 1-valued bits in a piece of data. This is based on the fact that 1 bits in RAM are charged capacitors that need to be refreshed often; as a result, the power consumed to refresh the RAM is proportional to the number of 1 bits. Similarly, the Hamming distance model states that an attacker can determine the number of bits that flipped values between two observations of a single piece of data. This is relevant for storage elements that consume most of their energy

not over time but when their stored value changes. In both cases, the model formalizes a *statistical correlation* between power consumption and the program's data by accounting for implementation details of the storage.

Models can also functionally capture non-functional properties like timing. For instance, RSA algorithms spend most of their time in modular exponentiation, and naive implementations perform varying numbers of modular multiplications depending on the value of the secret keys. This leads to a timing attack that observes the number of multiplications and thus part of the secret key [Koc96], which can be studied functionally.

However, at low levels of abstraction, non-functional elements tend to dominate. For example, timings can leak through instructions' interrupt latency [WMP21], data-dependent power policy (like Hertzbleed [Wan+22] monitoring Dynamic Voltage and Frequency Scaling), or just through speculative decisions not reflective of the program's code [Che+24].

So faults and side-channel models indicate how attackers may disturb or observe the system. The other piece of the puzzle for countermeasures is what needs protecting in the application.

# 2.2 Broad categories of security properties

Security properties formalize high-level security objectives such as *confidentiality*, *integrity*, or *availability* by specifying them within a given language or execution environment. There is no unified framework for this formalization, which leads to subtle variation between works; generally more so for properties related to fault tolerance compared to side-channels.

I want to draw attention to the fact that not all properties can be expressed at the same levels of abstraction: some are inherently low-level; some are high-level but may not translate well to low-level programs; a few are somewhat universal. This variety doesn't help with deriving a unified formalism.

**Functional correctness** The most common security property is *functional correctness*<sup>1</sup>: the requirement that the program behaves as per its original semantics even when attacked. It's the natural target for fault tolerance (although hard to reach!), and is implicit in many early works like SWIFT [Rei+05]. Side-channels never break it as they don't modify executions.

**Partial functional correctness** Most countermeasures detect faults *after* the program runs into an incorrect state. When no recovery is possible countermeasures allow erroneous outcomes, such as explicit termination, countermeasure-specific signals, or simply crashes. This idea of *partial correctness* generally comes with guarantees that the program stops "quickly" after an attack (with a suitable bound on the delay). This can satisfy security requirements when only chosen parts in a program are sensitive, such as the password check before the entry to a privileged section. For instance, NEMESIS [DSL17] detects attacks and stops the program when it's unable to recover.

Countermeasures against fault injections have a strong tendency to *default to functional correctness* as the only security property. I suspect this happens because of the field's background in *fault tolerance* (i.e. safety against faults), where there is no attacker and incorrect behavior is the only threat. Although not as obvious, fault injections can be used to threaten availability

<sup>&</sup>lt;sup>1</sup>Compiler people call this "safety", but here *safety* is security for non-targeted/random attacks.

or confidentiality all the same. In any case, for fault-related works that do not explicitly provide a security, some form of (partial) functional correctness should be assumed.

**Control flow integrity (CFI)** Control flow integrity is a family of properties about the integrity of execution paths taken by programs at runtime. They can appear at multiple levels:

- Within a function's CFG. Most commonly, control flow integrity refers to control following only valid edges of a function's control flow graph. Theißing et al. [The+13] list a number of countermeasures that achieve variations of this property with different types of checks.

- Within a sequential block. Instruction skips or arbitrary jumps might impact the execution of a sequential block (SSA basic block, C compound statement, or otherwise). Control flow integrity at this level is the property that all statements execute exactly in the source order.

- For a whole program. Control flow integrity can also extend to the inter-procedural level, requiring control to follow edges of the call graph much in the same way as a function's CFG edges [De 19].

### **Specialized forms of CFI** Weaker types of CFI may also be relevant:

- *Computation order*: the requirement for sensitive pure computation to occur in source order, such as refreshing the mask on a secret value. (See general literature on the analysis of masking, e.g. Prouff and Rivain [PR13]; the algorithms are very sensitive in general.)

- Interleaving: the CFI sub-scheme Step Counter Incrementation [HLB19] performs regular checks of a CFI witness value (the Step Counter) within sequential blocks. To be effective, the scheme requires the checks not be reordered relative to surrounding source code.

**Spatial or temporal redundancy** Programs or architectures can perform computations in redundant ways. This can be achieved by repeating work with the same resources but at a different time (*temporal* redundancy) [CRA06]. Another method is to use different resources (*spatial* redundancy), such as duplicated data [Gei+23] or silicon [Mar+21] (*lockstep* designs, often also with a time difference).

**Data erasure** The property that a given piece of data is unavailable in program memory at certain control points. This is tricky to do because almost every abstraction level redefines data storage in a way that allows previous values to remain in internal state that's functionally invisible, which requires control of low-level systems such as CPU registers. This problem occurs independently in many systems, such as in redundant file-system storage [ORK18].

**Non-interference** A common security property<sup>2</sup>, *non-interference* formalizes data confidentiality as the absence of dependence from a sensitive input to an observable output. The sensitive input may be functional, for instance when studying the influence of secrets on the statistical distributions of observable *probes* in a program [Bar+16]. It can also be nonfunctional, like micro-architectural state, which can often be observed indirectly and may require system-level support to eliminate [Bar+14a].

<sup>&</sup>lt;sup>2</sup>More specifically, a hyperproperty, since it is defined by quantifying over multiple executions.

The constant-time property The constant-time property is a ubiquitous non-interference property for timing side-channel resistance. It is usually defined as the absence of secret-dependent branches (observable by timing) or memory accesses (observable via cache). This characterization is surprisingly very functional as it can be studied at all abstraction levels between C and assembler, but has limits in the context of modern Spectre-style attacks because they reveal many more micro-architectural details [Cau+20]. When discussed at low levels "constant-time" may also exclude some secret-dependent computations on processors with e.g. variable-delay multiplication or division [Gau+23].

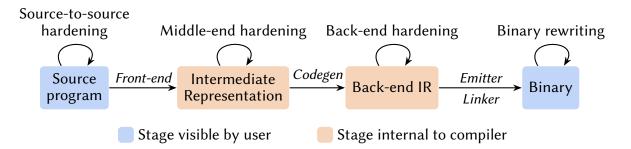

# 2.3 Techniques and design of hardening compilation

After starting mostly as source transformations in the early days of fault tolerance, countermeasures now consistently involve automatic transformation in compilers. Manual source protections do exist, most notably constant-time cryptographic implementations, but this practice doesn't scale to entire systems, other attack models, or non-functional security properties. Involving toolchains allows automated protection tuned to each attack model or target device, and gives access to internal program representations for transformation.

# 2.3.1 Hardening at every level in the toolchain

Depending on the type of countermeasure (and thus attack model and targeted security property), any stage of the compilation chain might be involved in hardening, as shown by Figure 2.2. However, I'd like to underline that no single level provides all desirable properties for countermeasures; usually either fine control of assembly or source annotations is missing. Works discussed in this section are summarized in Table 2.3, sorted by publication year.

Figure 2.2: Common compilation stages for hardening

**Source-to-source hardening** Countermeasures can be inserted by rewriting the source program (usually C) before compiling it.

Rebaudengo et al. [Reb+01] show an early example, targeted against transient memory errors, but claimed applicable to a wider range of transient faults. Their translation tool ThOR features standard transformations like duplicating variables, statements and function arguments; only returning from functions by address so return values can be duplicated; and control-flow integrity in the form of signature checks and duplicated conditions.

Lidman et al. [Lid+12] describe a recovery scheme for large-scale computing systems where they expect fault tolerance to allow undervolting machines for efficiency. Their countermeasure

| Cite     | Scheme            | Toolchain           | Hardening stage     | Attack model                           |

|----------|-------------------|---------------------|---------------------|----------------------------------------|

| [Reb+01] | ThOR              | N/A                 | Source-to-source    | "everything" (tests SEU <sup>†</sup> ) |

| [VHM03]  | ACFC              | gcc                 | Preprocessor        | Ins. skip/re-exec (multi-fault)        |

| [Rei+05] | SWIFT             | OpenIMPACT          | Assembler           | SEU <sup>†</sup>                       |

| [CRA06]  | SWIFT-R           | gcc 3.4.1 (PowerPC) | Early back-end      | SEU <sup>†</sup>                       |

| [CRA06]  | TRUMP             | gcc 3.4.1 (PowerPC) | Early back-end      | SEU <sup>†</sup>                       |

| [CRA06]  | MASK              | gcc 3.4.1 (PowerPC) | Early back-end      | SEU <sup>†</sup>                       |

| [Lid+12] | ROSE::FTTransform | N/A                 | Source-to-source    | "everything" (tests SEU†)              |

| [Bay+13] | Sleuth            | LLVM/Klee           | Back-end            | Leak info on ins. outputs              |

| [BCR16]  | unnamed           | LLVM 3.6 (ARM)      | Back-end            | Instruction skip                       |

| [DS16]   | nZDC              | LLVM 3.7 (ARMv8-a)  | Late back-end       | SEU <sup>†</sup> , "soft errors"       |

| [DSL17]  | NEMESIS           | LLVM 3.7 (ARMv8-a)  | Late back-end       | SEU <sup>†</sup> , wrong load/store    |

| [Pro+17] | unnamed           | LLVM 4.0 (ARM)      | Back-end (SSA IR)   | Ins. skip, reg. corruption             |

| [Boh+18] | COAST             | LLVM (MSP430)       | Late middle-end     | SRAM bit flip                          |

| [Van+18] | RACFED            | unknown             | Back-end CFG        | Bit flip in PC                         |

| [De 19]  | SecSwift          | LLVM                | Mostly middle-end   | Multiple control/data attacks          |

| [HLB19]  | unnamed           | N/A                 | Source-to-source    | Wrong/random jumps                     |

| [AA19]   | Smokestack        | LLVM 3.9            | Middle-end (+ libs) | Data-Oriented Programming              |

| [Kia+21] | unnamed           | LLVM (lifting)      | Binary rewriting    | SEU <sup>†</sup> , instruction skip    |

| [WMP21]  | unnamed           | (Secure)LLVM 13.0   | Back-end            | Leak interrupt delay                   |

| [Gei+23] | CompaSeC          | COMPAS (LLVM)       | Back-end            | Multi instruction skip                 |

| [Pes+25] | unnamed           | Chamois CompCert    | Middle-end (RTL)    | Branch inversion transition            |

†SEU: Single Event Upset (single bit flip in registers, memory, micro-architectural components...)

Table 2.3: Sample of hardening schemes implemented in or around a compiler

ROSE::FTTransform (implemented in the source-to-source compiler framework ROSE [QL11]) runs computations up to N times and selects results based on configurable policies.

More recently, Heydemann, Lalande, and Berthomé [HLB19] provide a verified CFI countermeasure against intra-procedural jumps or wrong function calls in C code. They use signature-based CFI with step counter incrementation to track the progress of each block, which can detect any jumps of at least two statements regardless of block size. Signatures are chosen globally (each function having a unique signature interval) so the scheme can also detect inter-procedural control flow faults.

The main benefit of source-to-source hardening is of course portability, while the crucial drawback is that the compiler can drastically alter security measures while compiling. This approach provides next to no control over assembly code and often requires disabling optimizations, which is slow and increases attack surface due to the larger code size.

**Compiler middle-end** Being the quintessential transformation pipeline in optimizing compilers, the middle-end is a natural choice for hardening.

Bohman et al. [Boh+18] evaluate an LLVM IR implementation of the Var3 scheme [Chi+12], called COAST, against neutron irradiation. Their countermeasure can duplicate or triplicate registers, computations and memory operations (but not control flow, although the implementation also independently supports CFCSS [OSM02]). Functional redundancy is typical for middle-end countermeasures, which don't have access to target-specific information. Despite the high cost, COAST causes a 7x mean-work-to-failure increase in the radiation setup.

SecSwift [De 19] implements slightly less usual transformations; it rewrites functions' prototypes to duplicate parameters and return values (which effectively modifies the ABI) and supports a dual intra-/inter-functional CFI scheme with signatures. The countermeasure is protected against back-end optimizations with intrinsics (I'll come back to that) and results in close to 100% coverage on random injection experiments.

Middle-end hardening can run after *most* optimizations while benefiting from typically superior documentation and language formalism than back-end representations. However, it can't easily relate to either source code or architectural details and still leaves all assembly code control to back-end algorithms.

**Compiler back-end and beyond** Countermeasures against low-level attack models are commonly implemented near the back-end, close to hardware.

Winderix, Mühlberg, and Piessens [WMP21] close an interrupt-based side-channel that leaks the execution times of instructions on simple microcontrollers. The countermeasure equalizes the traces of all possible control flow paths in the program with no-ops and silent copies of functions. This pass couldn't be performed before the back-end because earlier representations don't fix specific instruction traces; it can also hardly be performed on binaries directly due to the difficulty of inserting large amounts of new code in linked programs.

NEMESIS [DSL17] is a back-end triplication countermeasure inspired by SWIFT-R [CRA06], which uses three instruction streams as reference, error detection, and recovery respectively. I believe it covers all bit flips in registers, memory address corruptions, and memory operand corruptions, although its claim of detecting all "soft errors" has some openings.<sup>3</sup> NEMESIS has very detailed widgets and notably protects silent writes (no-op writes where the value written is also the value stored) against address corruption, which can't be detected by the usual precaution of re-reading written values.

My fetch skips countermeasure detailed in Chapter 4 [MDG24] reached the linker through ELF relocations. The scheme involves computing a checksum of assembly code, whose final encoding is not decided until the linker assigns explicit addresses to symbols. This could be performed on executables directly but only if it doesn't interact with any other relocation. I'll discuss more co-designed back-end countermeasures in Section 2.6.

Back-end hardening is the go-to choice for any countermeasure that handles low-level details and is quite effective as long as no source input is needed. Owing to the complexity of modern back-ends, most intra-functional transformations can be performed there, although the compiler's pipeline may be limiting.<sup>4</sup>

**Binary rewriting** A popular conservative approach is to rewrite output binaries; this bypasses the compiler and doesn't require access to source code.

Wenzl et al. [Wen+19] survey the mechanics of binary rewriting for different applications, including hardening against (mostly software) attacks. In each case, the binary is first analyzed using disassembly and structural recovery; it is then modified and reassembled using standard tools, sometimes even a production compiler. The survey highlights important variations in

<sup>&</sup>lt;sup>3</sup>In particular, it mentions instruction corruption as a potential threat, but changing the target register of an instruction can corrupt two execution streams at once. This leads, for example, to an attack that skips a memory write if the program writes the same value to memory multiple times, like e.g. memset() would do.

<sup>&</sup>lt;sup>4</sup>For example, in LLVM adding new code becomes impossible sometime before reaching assembly.

the analysis steps, as there doesn't appear to be popular widely-adopted tools in this area apart from reverse-engineering frameworks (IDA<sup>5</sup>, radare2<sup>6</sup>, etc.).

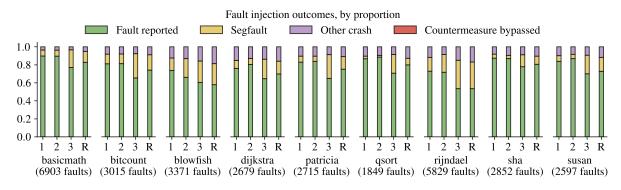

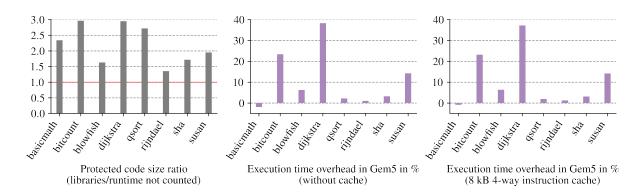

Binary rewriting isn't limited to simple transformations. Abromeit et al. [Abr+21] implement a masking countermeasure against side-channel attacks that observe secret-dependent data. This substitutes a number of elementary instructions with masking-compatible implementations known as *gadgets*, which requires moving some data to the stack and inserting calls to the gadgets. The paper performs these tasks almost entirely from an off-the-shelf binary, requiring only source-level annotations to identify secret variables.